标签

note

字数

1406 字

阅读时间

6 分钟

32 位 vs 64 位 CPU 64 位 CPU 的主要优势在于其一次性能处理 64 位(8 字节)的整数,并且能支持远大于 4GB 的内存寻址。

- 对于不超过 32 位(4 字节)的计算,两者性能差异不大。

- 只有在需要处理超过 32 位的超大数字或需要访问巨大内存时,64 位 CPU 的优势才能完全体现。

计算机的抽象模型

图灵机

图灵机是一个理论上的计算模型,它定义了一台抽象的计算机。其核心组件包括:

- 纸带 (Tape):相当于内存,可以无限长,用于存储数据。

- 读写头 (Head):可以在纸带上移动,并读写带上的符号,相当于文件 I/O。

- 控制单元: 根据当前状态和读到的符号,决定下一步的操作。

冯·诺依曼模型

现代计算机大多基于冯·诺依曼模型,其核心思想是存储程序(Stored-program Computer),即指令和数据都以二进制形式存储在内存中,可以被同等对待。

其五大核心组件是:

- 运算器 (ALU):负责执行算术和逻辑运算。

- 控制器 (Control Unit):负责指挥和协调计算机各部分工作。

- 存储器 (Memory):负责存放数据和指令。

- 输入设备 (Input Device):向计算机输入信息。

- 输出设备 (Output Device):从计算机输出信息。

为什么有了内存还需要寄存器? 因为 CPU 的计算速度远快于内存的读写速度。如果 CPU 每次都直接从内存存取数据,其性能会严重受限于内存速度。 寄存器 (Register) 位于 CPU 内部,紧邻控制器和运算器,访问速度极快,是 CPU 计算时使用的高速临时存储。

总线 (Bus)

总线是连接 CPU、内存和其它硬件设备的通信线路,负责它们之间的数据传输。主要分为三类:

- 地址总线 (Address Bus):用于指定 CPU 将要操作的内存地址。其宽度决定了 CPU 可寻址的内存空间大小(如 32 位地址总线可寻址 2^32 = 4GB 内存)。

- 数据总线 (Data Bus):用于在 CPU 和内存/其他设备之间传输数据。其宽度决定了 CPU 单次能传输的数据量(如 64 位数据总线一次可传输 8 字节)。

- 控制总线 (Control Bus):用于发送和接收各种控制信号,如时钟信号、中断请求、设备复位等。

CPU 的指令周期

CPU 执行程序的过程是一个不断循环的取指-执行周期。

- 取指 (Fetch):CPU 的控制单元根据程序计数器 (Program Counter, PC) 中存储的地址,通过地址总线从内存中读取指令,然后通过数据总线将指令存入指令寄存器 (Instruction Register, IR)。

- 译码 (Decode):CPU 分析指令寄存器中的指令,确定其操作类型和操作数。

- 执行 (Execute):

- 如果是计算类指令,交由逻辑运算单元 (ALU) 执行。

- 如果是存储类指令(读/写内存),由控制单元执行。

- 更新 PC: 程序计数器(PC)自增,指向下一条指令的地址。自增的大小取决于当前指令的长度。

示例:执行 a = 1 + 2

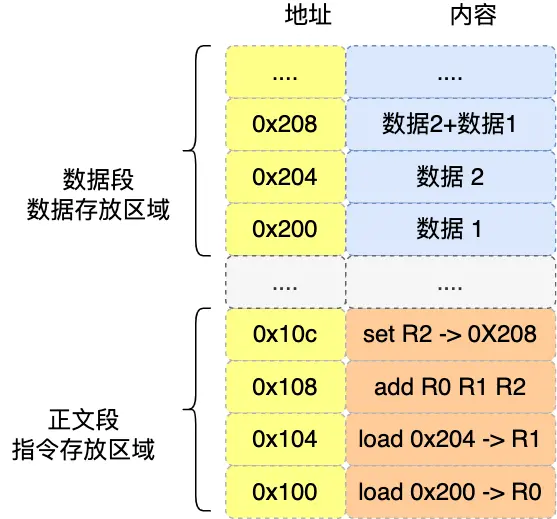

假设在 32 位 CPU 上执行 a = 1 + 2,编译器会将其翻译成多条机器指令。

- 编译阶段:

- 数据

1和2被存放在内存的数据段中,例如地址0x200和0x204。 - 变量

a的存储位置也被分配好,例如地址0x208。 a = 1 + 2这行代码被翻译成多条指令,存放在内存的代码段(正文段)中。

- 数据

- 执行阶段:

load 0x200, R0: 从地址0x200加载数据1到寄存器R0。load 0x204, R1: 从地址0x204加载数据2到寄存器R1。add R0, R1, R2: 将寄存器R0和R1的值相加,结果存入寄存器R2。store R2, 0x208: 将寄存器R2的结果(即3)存回地址0x208(变量a的位置)。

CPU 会依次执行这四条指令,完成 a = 1 + 2 的计算。

程序的执行速度

一个程序的 CPU 执行时间可以通过以下公式计算:

CPU 执行时间 = 指令数 × CPI × 时钟周期时间

- 指令数 (Instruction Count):执行程序所需的总指令数量。主要由编译器优化。

- CPI (Cycles Per Instruction):执行每条指令所需的平均时钟周期数。现代 CPU 通过流水线 (Pipeline) 技术,可以使得 CPI 的值接近 1,即平均一个时钟周期执行一条指令。

- 时钟周期时间 (Clock Cycle Time):即计算机主频的倒数。取决于硬件本身。超频就是缩短时钟周期时间,但会带来功耗和散热问题。